# Analysis of Power Dissipation and Thermal Considerations for High Voltage Gate Drivers

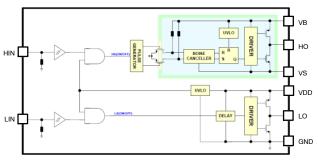

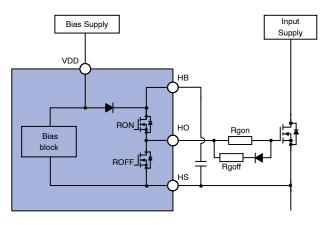

Gate drivers used to switch MOSFETs and IGBTs at high frequencies can dissipate significant amount of power depending on the operating conditions. It is important to determine the driver power dissipation and the resulting junction temperature in the application to ensure that the part is operating within acceptable temperature limits. High voltage gate drive IC (HVIC) is high side and low side gate drive IC designed for high-voltage, high-speed driving MOSFET for a half bridge switching application. Figure 1 shows the typical internal block diagram of HVIC. The main function blocks are the input stage, UVLO protections, level shifter and output driver stages. The gate driver losses include:

- Static losses related with static current at high and low side circuit blocks when driver is biased and not switching.

- Dynamic losses related with dynamic current when the switching signal is applied so linked to switching frequency.

- Gate driving losses related with load switch charges and also directly dependent on switching frequency.

Figure 1. Block Diagram of HVIC

The bootstrap diodes losses will not be discussed in this document because the current flowing the diode will be included in dynamic losses. However, one thing not to be overlooked is the instantaneous power loss to charge the bootstrap capacitor during start up. During this time a significant current can flow through the diode to quickly charge the bootstrap capacitor and can generate relatively high losses during several switching periods. The bootstrap diode must withstand this current and power loss and this loss will add to driver internal power losses when this diode is.

# ON Semiconductor®

www.onsemi.com

# APPLICATION NOTE

### **Static Power Loss Analysis**

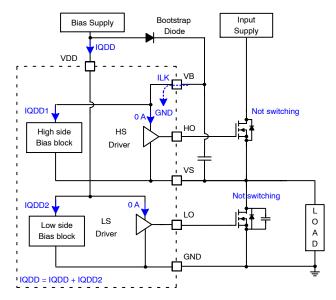

The Figure 2 shows a simplified schematic of the half bridge switch network associated with high and low side driver to explain the static losses.

Figure 2. Simplified Circuit Diagram of Driver and Half-bridge Configuration for Static Power Losses

The static losses are due to the quiescent currents from dc voltage supplies  $V_{DD}$  to ground in the low-side driver and the leakage current in the level shifter in the high-side driver as described by the following equations.

$$P_{Static} = P_{Quiescent} + P_{Leakage}$$

(eq. 1)

$$P_{Quiescent} = V_{DD} \times I_{QDD}$$

(eq. 2)

$$P_{Leakage} = V_{BOOT} \times I_{LK}$$

(eq. 3)

Where,  $I_{QDD}$  is the quiescent current under no input switching signal,  $V_{BOOT}$  is the boot voltage at high side and  $I_{LK}$  is the leakage current at boot pin (HB pin in Figure 2). The static power loss are permanent as soon as the driver is powered and by definition are not related to the frequency of the input signals.

However, most of power losses occur when the driver is turning On and Off the power switches. Hence,  $I_{QDD}$  is included in the operating current during switching mode, so  $P_{Quiescent}$  should not be considered in this case.  $P_{Leakage}$  should be considered in the case that  $I_{LK}$  is not small enough to be neglected and/or when  $V_{BOOT}$  level is very high such as in 1,200 V drivers. Most of the time,  $I_{LK}$  is not provided in the driver datasheet. In this case,  $P_{Leakage}$  can be ignored and is generally very small compared to others losses.

# **Dynamic Power Loss Analysis**

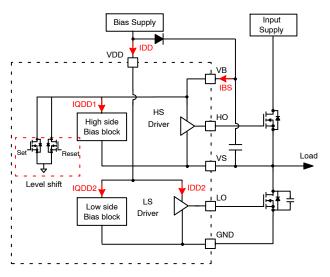

Let's consider now the predominant loss sources. Figure 3 shows the circuit diagram of driver IC to address dynamic losses. The first dynamic loss is defined as the losses in the level shift (LS) in high side drive, P<sub>LS</sub>.

$$P_{LS} = (V_{R} + V_{DD} - V_{DBOOT}) \times Q_{internal} \times f_{SW}$$

(eq. 4)

Figure 3. Simplified Circuit Diagram of Driver and Half-bridge Configuration for Dynamic and Power Losses

$V_R$  is a boot pin voltage between VB and GND and  $V_{DBOOT}$  is the forward voltage drop of the bootstrap diode.  $Q_{internal}$  is the total gate charge of the internal LDMOS used in the level shift circuit.  $Q_{internal}$  specification is not normally provided from manufacturer so not found in the datasheet. In this case as a rule of thumb  $Q_{internal}$  value could be estimated around  $2{\sim}3$  nC for 600 V high side drivers and  $0.5{\sim}1$  nC for 100-200 V drivers. Some driver products using old technology might have relatively high  $Q_{internal}$ , so  $P_{LS}$  should be taken into account at high frequency operation, but in recent state of art drivers, this value is getting lower and lower so the losses can be neglected if no  $Q_{internal}$  realistic value is available.

The second dynamic loss are internal losses on  $V_{DD}$  and HB pins due to the operating current when the output signals are switching On and Off the external switches and is given by below equation:

$$P_{OP} = V_{DD} \times I_{DD} + (V_{DD} - V_{Didode}) \times I_{BS}$$

(eq. 5)

$I_{DD}$  is the operating current on  $V_{DD}$  and  $I_{BS}$  is the operating current at high side driver pin, VB.  $V_{Diode}$  is the forward voltage drop of bootstrap diode. This power loss is resulting from internal current consumption under dynamic operating conditions. The internal current  $I_{DD}$  and  $I_{BS}$  should be determined under actual operating conditions referring to datasheet parameters taking into account for switching frequency and temperature variation.

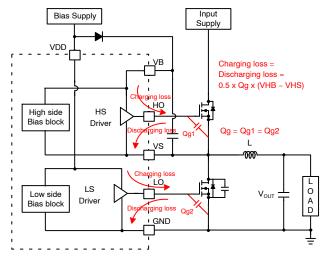

Figure 4. Simplified Circuit Diagram of Driver and Half-bridge Configuration for Gate Driving Power Losses

# **Gate Driving Loss Analysis**

The gate driving loss in the driver is the most significant power loss resulting from supplying gate current to switch the load MOSFET *On* and *Off* at the switching frequency. The gate driving losses are coming from charging and discharging the load capacitor (for MOSFET, the load capacitor is the input capacitor of MOSFET) and expressed by the following equation.

$$P_{charging} = P_{discharging} = 0.5 \times V_{DD} \times Q_g \times f_{sw}$$

(eq. 6)

Where,  $Q_g$  is the total gate charge of the external MOSFET and  $f_{sw}$  denotes the switching frequency. In case of a soft switching topology,  $Q_g$  is equal to gate to source charge  $(Q_{gs})$  of the FET or IGBT. The total gate driving losses in high and low side drivers is then 4 times  $P_{charging}$ .

$$P_{gate\_driving} = 2 \times V_{DD} \times Q_g \times f_{sw}$$

(eq. 7)

Since the major power loss is the gate driving loss, the simplest and fastest way to calculate the losses in a driver is to sum the gate driving loss ( $P_{gate\_drving}$ ) and dynamic losses on  $V_{DD}$  ( $P_{VDD}$ ).

These losses acount for more than 90% in recent middle voltage class high and low side driver products.

### **Thermal Analysis**

Once the power dissipated inside the driver is calculated, we can estimate the junction temperature of the driver. This can be evaluated assuming thermal resistance or characterization was determined for a similar thermal design (heat sinking and air flow). The thermal equation is:

$$T_{J} = P_{TOTAL} \times R_{jx} \times T_{x}$$

(eq. 8)

### Where:

$T_J$  = the junction temperature of driver die

$R_{jx}$  = thermal resistance ( $\theta$ ) or characterization parameter ( $\Psi$ ) relating temperature rise to total power dissipation

$T_x$  = temperature of point x as defined in the thermal characteristic table from datasheet.

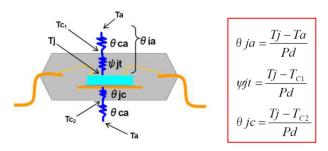

The thermal information is shown in Figure 5 and Table 1. Thermal characteristic of the package is a function of several parameters such as geometry, boundary condition, test condition, etc. This requires numerical analytical tool or modeling technique that are generally cumbersome to manipulate. It can be tricky to estimate the junction temperature precisely with thermal information coming from datasheet.

So it is helpful to review the definition of thermal information.

- 1. θja is the Junction-to-Air Thermal Resistance. It measures theheat flow between the die junction and the air. It is mainly relevant for packages used without any external heat sink.

- θjc is the Junction-to-Case Thermal Resistance and it measures the heat flow between the die junction and the surface of the package. It is mainly relevant for packages using some external heat sinks

- 3. Ψjt is the Junction-to-PKG Top Thermal Characterization Parameter and it provides correlation between die temperature and temperature of package topside. This can be used to estimate die temperature in applications

- 4. Ψjb is the Junction-to-Board Thermal Characterization Parameter and it provides correlation between die temperature and board temperature. This can be used to estimate die temperature in applications.

Figure 5. Thermal Resistance and Characterization Parameters with Package

Table 1. DEFINITION OF THERMAL RESISTANCE AND CHARACTERIZATION PARAMETERS

| Item            | Definitions                                       |  |

|-----------------|---------------------------------------------------|--|

| θја             | Thermal resistance between Tj and Ta              |  |

| Ψjt             | Thermal resistance between Tj and T <sub>C1</sub> |  |

| θјс             | Thermal resistance between Tj and T <sub>C2</sub> |  |

| θса             | Thermal resistance between Tc and Ta              |  |

| Tj              | Junction temperature                              |  |

| Та              | Ambient temperature                               |  |

| T <sub>C1</sub> | Temperature of the top surface of IC package      |  |

| T <sub>C2</sub> | Temperature of the bottom surface of IC package   |  |

| Pd              | Maximum permissible powe                          |  |

Generally, the thermal information provided in semiconductor datasheet can't cover all applications cases. For the following examples we'll only use  $\theta$ ja for Tj calculation.

For more details on how to properly use thermal data found in datasheet, please refer to detailed Application notes: <a href="https://www.onsemi.com/pub/Collateral/AND8220-D.PDF">www.onsemi.com/pub/Collateral/AND8220-D.PDF</a>.

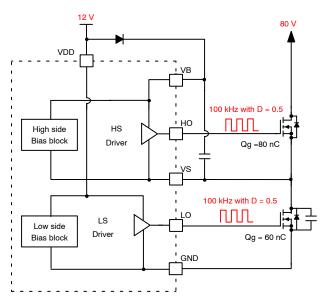

### **Application to NCV51511**

NCV51511 power loss calculation and thermal estimation will be developed in this section. The total power dissipation is calculated under below conditions:

- Ambient temperature: 25°C

- $V_{DD} = 12 \text{ V} \text{ and } V_B = 80 \text{ V}$

- Switching frequency = 100 kHz

- Gate resistance  $R_g = 0 \Omega$

- Q<sub>G</sub> of external MOSFET is 80 nC

The circuit implementation is depicted in Figure 6.

1. Static losses are calculated by leakage current in the level shift stage at VB pin.

$$\label{eq:planet} P_{Leakage} \,=\, V_{BOOT} \,\times\, I_{LK} \,=\, 80 \; V \,\times\, 10 \;\mu\text{A} \,=\, 0.8 \;\text{mW} \\ \text{(eq. 9)}$$

This static loss in high side section can be ignored as the leakage current is small and  $V_{BOOT}$  is low for this driver.

Dynamic losses can be estimated by the level shifting circuit and operating the operating current associated with internal CMOS circuitry.

$$P_{LS} = (V_R + V_{DD} - V_{DBOOT}) \times Q_{internal} \times f_{sw} =$$

$$= (80 V + 12 V - 1 V) \times 0.48 \text{ nC} \times 100 \text{ kHz} =$$

$$= 4.368 \text{ mW}$$

(eq. 10)

The dynamic loss on level shift is described in the appendix in detail. To calculate this power loss exactly, the key information normally not shown in the datasheet are needed such as gate charge of high voltage MOSFET for level shift (Q<sub>internal</sub>). This power loss is not completely negligible, but the amount of power is still small.

# AND90004

$$\begin{split} P_{VDD} &= V_{DD} \times I_{DDO} + (V_{DD} - V_{Diode}) \times I_{BSO} = \\ &= 12 \text{ V} \times 0.5 \text{ mA} + 11 \text{ V} \times 0.5 \text{ mA} = 11.5 \text{ mW} \end{split}$$

(eq. 11)

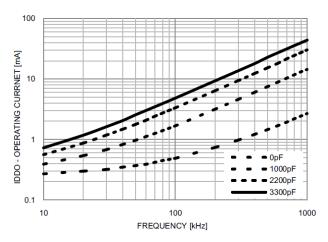

The operating current must be taken as shown in datasheet characteristic curve like the Fig. 6 considering the frequency and load capacitance

Figure 6. I<sub>DD</sub> Operating Current vs. Frequency

Figure 7. Half-bridge Configuration for the Case Study

3. Gate driving losses can be calculated by

$$\begin{aligned} \text{P}_{\text{gate\_driving}} &= 2 \times \text{V}_{\text{DD}} \times \text{Q}_{\text{g}} \times \text{f}_{\text{sw}} = 2 \times 12 \,\text{V} \times \\ &\times \text{80 nC} \times \text{100 kHz} = \text{192 mW} \end{aligned} \tag{eq. 12}$$

4. Total power losses is the summation of 1 and 2 and 3.

$$P_{total} = P_{Leakage} + P_{LS} + P_{VDD} + P_{gate driving} =$$

$$= 0.8 \text{ mW} + 4.4 \text{ mW} + 11.5 \text{ mW} + 192 \text{ mW} =$$

$$= 208.7 \text{ mW}$$

(eq. 13)

The total power dissipation of NCV51511 in this operating conditions is 209 mW and the majority of power loss comes from gate driving loss that represents 92% of power loss and 5.5% power loss is generated by dynamic losses at Vdd and VB pin. So 97.5% power losses can be obtained by the following.

$$P_{(97\% \text{ of total})} = 2 \times V_{DD} \times Q_g \times f_{sw} + V_{DD} \times (I_{DDO} + I_{BSO})$$

(eq. 14)

All parameters to calculate about 97% power dissipation could be quickly found in the datasheet and the application conditions. So as a rule of thumb, the total IC power dissipation could be gate driving loss neglecting the static losses and level shift loss in middle voltage gate driver.

Once the power dissipation is estimated, the junction temperature can be predicted using the thermal resistance described in the datasheet. The Table 2 shows the thermal characteristics of NCV51511 that is housed into SOIC–8 package with exposed pad (EP). EP can certainly improve the thermal performance hence the thermal resistance is way smaller than standard SOIC–8. The thermal resistance of junction to air ( $\theta_{JA}$ ) of NCV51511 is 39°C/W while the general SOIC–8 is between 150~200°C/W.

**Table 2. THERMAL INFORMATION OF NCV51511**

| Symbol | Parameter                                              | Value | Unit |

|--------|--------------------------------------------------------|-------|------|

| θЈА    | Thermal Resistance Junction-Air *                      | 39    | °C/W |

| ΨJL    | Thermal characterization parameter Junction-Lead       | 15    | °C/W |

| ΨJT    | Thermal characterization parameter Junction–Case (TOP) | 6     | °C/W |

\*As mounted on a 76.2 x 114.3 x 1.6 mm FR4 substrate with a Multi-layer of 1 oz copper traces and heat spreading area. As specified for a JEDEC 51-7 conductivity test PCB. Test conditions were under natural convection or zero air flow

These thermal information offers various approaches to estimate junction temperature using following equations when the ambient, package lead or case top temperature are measured or given. It could be that there would be small difference between the calculation and real junction temperature. Measurement set up from the information of datasheet (JEDEC) is not identical to the real application such as the PCB material and trace copper thickness and area or even the number of total PCB layer but still it gives a close enough estimation to help designers to know the thermal margin they have.

- Total power dissipation = 209 mW.

- If  $\theta_{JA}$  and Ta are given

$$T_J = Pd \times \theta_{JA} + Ta = 0.21 \times 39 + Ta = 8.19 + Ta (^{\circ}C)$$

(eq. 15)

If Ψ<sub>JL</sub> is known and lead temperature can be measured (T<sub>Lead</sub>)

$$\begin{split} T_J &= Pd \times \ \Psi_{JL} + T_{Lead} = 0.21 \times 15 + T_{Lead} \,^{\circ}C \ = \\ &= 3.15 + T_{Lead} \,^{(\circ}C) \end{split} \tag{eq. 16}$$

• If  $\Psi_{JT}$  is known and case-top temperature can be measured ( $T_{Top}$ )

$$\begin{split} T_{J} &= \text{Pd} \times \Psi_{JT} + T_{Top} = 0.21 \times 6 + T_{Top} \,^{\circ}\text{C} &= \\ &= 1.26 + T_{Top} \,^{(\circ}\text{C}) \end{split} \tag{eq. 17}$$

This estimation of the junction temperature (Tj) provide useful guidance to take any action if Tj is getting too close to the max recommended operating temperature range described in the datasheet.

# **Application to NCV5183**

As another example, NCV5183 power loss calculation and thermal estimation is described below. The total power dissipation is calculated under below conditions:

- Ambient temperature: 25°C

- $V_{DD} = 12 \text{ V} \text{ and } V_B = 400 \text{ V}$

- Switching frequency = 50 kHz

- Gate resistance  $R_g = 0 \Omega$

- Q<sub>G</sub> of external MOSFET is 80 nC.

- 1. Static losses are calculated by leakage current in the level shift stage at VB pin.

$$P_{Leakage} = V_{BOOT} \times I_{LK} = 400 \text{ V} \times 1 \text{ } \mu\text{A} = 0.4 \text{ mW}$$

(eq. 18

Actually, the leakage current specification isn't provided in the datasheet and this static loss in high side can be ignored

2. Dynamic losses for level shift circuit and the operating power loss

$$P_{LS} = (V_R + V_{DD} - V_{DBOOT}) \times Q_{internal} \times f_{sw} =$$

$$= (400 V + 12 V - 1 V) \times 0.82 \text{ nC} \times 50 \text{ kHz} =$$

$$= 16.85 \text{ mW}$$

(eq. 19)

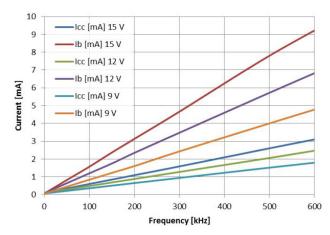

Q<sub>internal</sub> is also not given from datasheet. As a rule of thumb this is generally way below 1 nC for 100 V so negligible and between 1 and 3 nC for 600 V drivers. So this loss is not totally negligible since the boot voltage is high and frequency is also not low. The operating power loss.

$$P_{VDD} = V_{DD} \times I_{DDO} + (V_{DD} - V_{Diode}) \times I_{BSO} =$$

= 12 V × 0.4 mA + 11 V × 0.7 mA = 12.5 mW

(eq. 20)

The operating current are taken as shown in datasheet characteristic curve as below.

Figure 8. I<sub>DD</sub> Operating Current vs. Frequency

3. Gate driving losses can be calculated by

$$\begin{aligned} \text{P}_{\text{gate\_driving}} &= 2 \times \text{V}_{\text{DD}} \times \text{Q}_{\text{g}} \times \text{f}_{\text{sw}} = 2 \times 12 \,\text{V} \times \\ &\times 80 \,\text{nC} \times 50 \,\text{kHz} = 96 \,\text{mW} \end{aligned} \tag{eq. 21}$$

The factor 2 is to take into account low and high side drive losses.

4. Total power losses is the summation of 1 and 2 and 3

$$P_{total} = P_{Leakage} + P_{LS} + P_{VDD} + P_{gate driving} =$$

$$= 0.4 \text{ mW} + 16.8 \text{ mW} + 12.5 \text{ mW} + 96 \text{ mW} =$$

$$= 125.7 \text{ W}$$

(eq. 22)

The total power dissipation of NCV5183 in this operating conditions is 126 mW and the majority of power loss still comes from  $P_{gate\ driving}$  and accounts for ~77% and  $P_{OP}$  is 10%. So 87% power losses can be easily obtained by the following.

$$P_{(97\% \text{ of total})} = 2 \times V_{DD} \times Q_g \times f_{sw} + V_{DD} \times (I_{DDO} + I_{BSO})$$

(eq. 23)

NCV5183 only provides  $\theta_{JA}$  183°C/W which is high thermal resistance because it is a standard SOIC-8 package.

- Total power dissipation = 125 mW

- $\bullet$   $\theta_{JA}$  and Ta are given

$$T_J = Pd \times \theta_{JA} + Ta = 0.125 \times 183 + Ta =$$

= 22.87 + Ta (°C) (eq. 24)

So in these conditions we can estimate that the internal die temperature will be 23°C higher than ambient.

# AND90004

# **Application to NCP51530**

As third example, NCP51530 is chosen and operating conditions are as below

- $V_{DD} = 15 \text{ V}$  and  $V_{B} = 400 \text{ V}$

- Switching frequency = 100 kHz

- Gate resistance  $R_g=0$   $\Omega$

- Q<sub>G</sub> of external MOSFET is 30 nC

- 1. Static losses.

$$\label{eq:planet} P_{Leakage} \,=\, V_B^{} \,\times\, I_{LK}^{} \,=\, 400~V \,\times\, 6~\mu A \,=\, 2.4~mW \endalign{\mbox{\em (eq. 25)}}$$

The leakage current are specified in the datasheet as  $I_{\mbox{\scriptsize HBO}}$ .

2. Dynamic losses

$$P_{LS} = (V_B + V_{DD} - V_{DBOOT}) \times Q_{internal} \times f_{sw} =$$

$$= (400 V + 15 V - 1 V) \times 1 nC \times 100 kHz =$$

$$= 41.4 mW$$

(eq. 26)

$$P_{VDD} = V_{DD} \times I_{DDO} + (V_{DD} - V_{Diode}) \times I_{BSO} =$$

= 15 V × 0.4 mA + 14 V × 0.7 mA = 15.8 mW

(eq. 27)

3. Gate driving losses

$$\begin{aligned} P_{gate\_driving} &= 2 \times V_{DD} \times Q_g \times f_{sw} = 2 \times 15 \text{ V} \times \\ &\times 30 \text{ nC} \times 100 \text{ kHz} = 90 \text{ mW} \end{aligned} \tag{eq. 28}$$

4. Total power losses.

$$P_{total} = P_{Leakage} + P_{LS} + P_{VDD} + P_{gate driving} =$$

$$= 2.4 \text{ mW} + 41.4 \text{ mW} + 11.6 \text{ mW} + 90 \text{ mW} =$$

$$= 150 \text{ W}$$

(eq. 29)

The total power dissipation is calculated as 150 mW.  $\theta_{JA}$  shows with 145°C/W for 8SOIC and 72°C/W for DFN10.

$\bullet$   $\theta_{JA}$  and Ta are given

$$T_{J} = Pd \times \theta_{JA(8SOIC)} + Ta = 0.15 \times 145 + Ta =$$

$$= 21 + Ta \, (^{\circ}C) \eqno(eq. 30)$$

# Application to FAN73912

A final example is FAN73912 and operating conditions are as below

- $V_{DD} = 20 \text{ V} \text{ and } V_B = 800 \text{ V}$

- Switching frequency = 20 kHz

- Gate resistance  $R_g = 0 \Omega$

- Q<sub>G</sub> of external MOSFET is 10 nC

- 1. Static losses

The leakage current are specified in the datasheet as I<sub>SD</sub>.

2. Dynamic losses

$$\begin{split} P_{LS} &= (V_{B} + V_{DD} - V_{DBOOT}) \times Q_{internal} \times f_{sw} = \\ &= (800 \text{ V} + 20 \text{ V} - 1 \text{ V}) \times 1.5 \text{ nC} \times 20 \text{ kHz} = \\ &= 24.6 \text{ mW} \\ \\ P_{VDD} &= V_{DD} \times I_{DDO} + (V_{DD} - V_{Diode}) \times I_{BSO} = \\ &= 20 \text{ V} \times 0.1 \text{ mA} + 19 \text{ V} \times 2 \text{ mA} = 40 \text{ mW} \end{split}$$

3. Gate driving losses

$$\begin{aligned} \mathsf{P}_{\mathsf{gate\_driving}} &= 2 \times \mathsf{V}_{\mathsf{DD}} \times \mathsf{Q}_{\mathsf{g}} \times \mathsf{f}_{\mathsf{sw}} = 2 \times 20 \,\mathsf{V} \times \\ &\times 10 \,\mathsf{nC} \times 20 \,\mathsf{kHz} = 8 \,\mathsf{mW} \end{aligned} \tag{eq. 35}$$

(eq. 34)

4. Total power losses

$$P_{\text{total}} = P_{\text{Leakage}} + P_{\text{LS}} + P_{\text{VDD}} + P_{\text{gate driving}} =$$

$$= 24 \text{ mW} + 24.4 \text{ mW} + 40 \text{ mW} + 8 \text{ mW} =$$

$$= 96.4 \text{ W}$$

(eq. 36)

The total power dissipation is 96.6 mW and  $\theta_{JA}$  shows with 95°C/W for 14SOIC.

$\theta_{JA}$  and Ta are given

$$T_J = Pd \times \theta_{JA(8SOIC)} + Ta = 0.096 \times 95 + Ta =$$

$$= 9.1 + Ta (^{\circ}C)$$

(eq. 37)

# Recommendations to Reduce Ti

In case Tj is too close to the recommended operating temperature, there are few things that could be considered.

- 1. Add external gate resistors to distribute the power losses: When no external gate resistor is inserted between the driver and MOSFET, the power is entirely dissipated inside the driver package. Using external gate resistor allows to share the power losses between the internal gate resistance of driver and the inserted external resistor. The split is given by the ratio between the 2 resistors. The higher the external gate resistor is the less power dissipation happen inside the driver.

- 2. Reduce the switching frequency. The switching frequency is affecting most of the power losses so it could help whenever the application allows it.

- 3. Use heat sink. Enlarge PCB area and add more copper around the driver.

- 4. Reduce supply voltage VDD if possible. Latest generations of drivers and MOSFET's offer this option.

Reducing the switching frequency or supply voltage is not always possible and enlarge the PCB or add heat dissipation means is often limited. Most of the time one uses external gate resistors for various reasons such as limit ringing caused by parasitic or high dV/dt, tune gate drive strength to reduce EMI. This also has an impact on the power losses distribution. By adding external gate resistor, the gate driving power loss will be calculated as follow:

$$P_{sw} = Q_g \times V_{DD} \times f_{sw} \times \left(\frac{RON}{RON + Rgon} + \frac{ROFF}{ROFF + Rgoff}\right)$$

(eq. 38)

Where,  $R_{ON}$  and  $R_{OFF}$  are the resistance value of internal pull up and down structures and  $R_{gon}$  and  $R_{goff}$  are the external gate resistors. Simply, if  $R_{ON} = R_{OFF} = Rg$ , the Psw will be the half of the total power dissipation compared with no external gate resistance.

Figure 9. Internal Pull Up and Down Resistance

As an illustration for NCV51511, Ron is 4  $\Omega$  and Roff is 2  $\Omega$  from the calculation of Vdd/peak pull up (or down) current. If 2  $\Omega$  is inserted between output pins and the MOSFET gate, the gate driving losses is down to 83%.

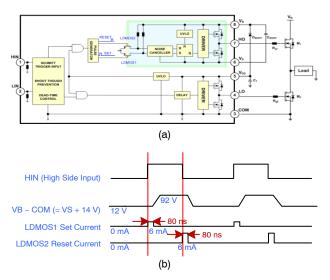

## **Power Dissipation in the Level Shift Circuit**

Figure 10 shows the typical internal block diagram associated with level shift and timing diagram. To maintain high efficiency operation and manageable power dissipation, the level shifters should not draw any current during the on–time of the main switches. The level shift shown in Figure 10 (a) is widely used technique called pulsed latch level transistors.

Figure 10. (a) Typical Internal Block Diagram of HVIC. (b) Associated Waveform of Level Shift

To calculate the power dissipation in the level shifter, we assume the test conditions are the same as NCV51511 case study: Temp = 25°C,  $V_{DD}$  = 12 V,  $V_{DBOOT}$  = 1 V,  $V_{R}$  = 80 V, Freq = 100 kHz,  $T_{on}$  = 80 ns, and  $I_{d}$  = 6 mA for level shift circuit.

Qp of Set and Reset can estimated

$$SetQ_P = Isubd \times T_{ON} = 6 \text{ mA} \times 80 \text{ ns} = 0.48 \text{ nC}$$

(eq. 39

$$ResetQ_P = Isubd \times T_{ON} = 6 \text{ mA} \times 80 \text{ ns} = 0.48 \text{ nC}$$

(eq. 40)

From the Qp, the power dissipation for the case of set and reset period.

$$P_{D,set} = (V_{DD} - V_{DBOOT}) \times Q_{P} \times Freq = 11 \text{ V} \times 0.48 \text{ nC} \times \\ \times 100 \text{ kHz} = 0.57 \text{ mW}$$

(eq. 41)

$$P_{D,reset} = (V_R + V_{DD} - V_{DBOOT}) \times Q_P \times Freq = 91 \text{ V} \times \\ \times 0.48 \text{ nC} \times 100 \text{ kHz} = 4.37 \text{ mW}$$

(eq. 42)

The total power dissipation of level shift is the sum of  $P_{d,set}$  and  $P_{d,reset}$ . Here,  $P_{d,set}$  is significantly smaller than  $P_{d,rest}$ , we can ignore  $P_{d,set}$  and simply take into account  $P_{d,rest}$ .

ON Semiconductor and ware trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices with a same or similar classification in a foreign jurisdiction or any devices with a same or similar classification in a foreign jurisdiction or any devices with a same or similar clas

### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910

$\textbf{ON Semiconductor Website:} \ \underline{www.onsemi.com}$

For additional information, please contact your local Sales Representative